The NASA Electronic Parts and Packaging (NEPP) Program is working to further advance packaging technology that has become a critical feature of modern Electrical, Electronic, Electromechanical and Electro-optical (EEEE) parts. In collaboration with its academic partner, Georgia Tech, the NEPP Program is exploring 2.5/3D glass substrate technology for space applications.

“The heterogeneous evolution of modern commercial packaging technologies into 2.5 and 3D variants has continued at a double-digit rate of growth each year for over a decade now,” said Doug Sheldon, Assurance Technology Program Office program manager and NEPP Senior Staff member, Jet Propulsion Laboratory. “The benefits of being able to infuse such technologies into NASA missions is substantial.”

In the past eight years, EEEE parts packaging technology made more significant advances than it had in the preceding 30 years of development. In the past, EEEE parts packages used in NASA missions typically were thought of as single pieces of silicon with bond pads connected via bond wires to a ceramic enclosure.

These days, that image is significantly more complex. Where there used to be a single piece of silicon in a package, now there are often four or more different die. In many cases, these dies are completely different pieces of silicon with separate functionalities, such as processing or memory. In some cases, the die is made from different materials such as silicon or Gallium Nitride.

Bond wires and pads are now generalized into concept of interconnects, which can then be treated as a scaling variable to measure technological progress. Current generations of space packaging technologies measure interconnect density in terms of 100s of interconnects/mm2, whereas modern 2.5D/3D packaging routinely are capable of 1,000s to 10,000s of interconnects/mm2.

Heritage ceramic packages were first replaced by organic substrates made up of complex combinations of nonconductive glass fibers and epoxy resins. As the demands for interconnect density, device speed and related bandwidth continued to increase, glass substrate technology has now begun to challenge these commercial organic substrates.

“The glass substrates allow for improvement to device size, weight and power and also allow for integrations of different die technologies,” said Sheldon.

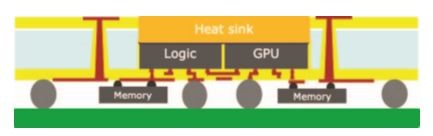

Figure 1. 3D Glass Panel Embedded package for high performance computing

The NEPP Program and Georgia Tech are working together to understand the fitness for space of glass substrate and their related technologies. For example, in Figure 1, the 3D glass panel has three different functional silicon die: Graphics Processing Unit, logic and memory. The memory die minimizes the interconnection length and only requires very fine (<10um) distance between connections. An added heat sink can manage important thermal concerns that arise from having the three different high-performance die placed in such a small physical area.

“These new packaging technologies enable the high-performance computer power that NASA requires for future on-orbit edge-based Artificial Intelligence and Machine Learning applications,” said Sheldon. “The partnership with Georgia Tech gives us access to state-of-the-art technology and allows us to join the next generation of advanced packaging.”

The NEPP Program generates technical knowledge and recommendations about EEEE part performance, application, failure modes, test methods, reliability and supply chain quality within the context of NASA space flight missions and hardware.

For more information, visit the NEPP website or contact Sheldon.